ARC® 700 IP Library

# **ARC® 700 External Interfaces**

Reference

5117-014

#### **ARC® 700 External Interfaces Reference**

#### **ARC®** International

European Headquarters ARC International, Verulam Point, Station Way, St Albans, Herts, AL1 5HE, UK Tel. +44 (0) 1727 891400 Fax. +44 (0) 1727 891401 North American Headquarters 3590 N. First Street, Suite 200 San Jose, CA 95134 USA Tel. +1 408.437.3400 Fax +1 408.437.3401

www.arc.com

#### **ARC Confidential Information**

© 2003-2008 ARC International (Unpublished). All rights reserved.

#### Notice

This document, material and/or software contains confidential and proprietary information of ARC International and is protected by copyright, trade secret, and other state, federal, and international laws, and may be embodied in patents issued or pending. Its receipt or possession does not convey any rights to use, reproduce, disclose its contents, or to manufacture, or sell anything it may describe. Reverse engineering is prohibited, and reproduction, disclosure, or use without specific written authorization of ARC International is strictly forbidden. ARC and the ARC logotype are trademarks of ARC International.

The product described in this manual is licensed, not sold, and may be used only in accordance with the terms of a License Agreement applicable to it. Use without a License Agreement, in violation of the License Agreement, or without paying the license fee is unlawful.

Every effort is made to make this manual as accurate as possible. However, ARC International shall have no liability or responsibility to any person or entity with respect to any liability, loss, or damage caused or alleged to be caused directly or indirectly by this manual, including but not limited to any interruption of service, loss of business or anticipated profits, and all direct, indirect, and consequential damages resulting from the use of this manual. ARC International's entire warranty and liability in respect of use of the product are set forth in the License Agreement.

ARC International reserves the right to change the specifications and characteristics of the product described in this manual, from time to time, without notice to users. For current information on changes to the product, users should read the "readme" and/or "release notes" that are contained in the distribution media. Use of the product is subject to the warranty provisions contained in the License Agreement.

Licensee acknowledges that ARC International is the owner of all Intellectual Property rights in such documents and will ensure that an appropriate notice to that effect appears on all documents used by Licensee incorporating all or portions of this Documentation.

The manual may only be disclosed by Licensee as set forth below.

- Manuals marked "ARC Confidential & Proprietary" may be provided to Licensee's subcontractors under NDA. The manual may not be provided to any other third parties, including manufacturers. Examples--source code software, programmer guide, documentation.

- Manuals marked "ARC Confidential" may be provided to subcontractors or manufacturers for use in Licensed Products. Examples-product presentations, masks, non-RTL or non-source format.

- Manuals marked "Publicly Available" may be incorporated into Licensee's documentation with appropriate ARC permission. Examples--presentations and documentation that do not embody confidential or proprietary information.

The ARCompact instruction set architecture processor and the ARChitect configuration tool are covered by one or more of the following U.S. and international patents: U.S. Patent Nos. 6,178,547, 6,560,754, 6,718,504 and 6,848,074; Taiwan Patent Nos. 155749, 169646, and 176853; and Chinese Patent Nos. ZL 00808459.9 and 00808460.2. U.S., and international patents pending.

#### **U.S. Government Restricted Rights Legend**

Use, duplication or disclosure by the U.S. Government is subject to restrictions as set forth in FAR 52.227.19(c)(2) or subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 and/or in similar or successor clauses in the FAR, or the DOD or NASA FAR Supplement.

CONTRACTOR/MANUFACTURER IS ARC International I. P., Inc., 3590 N. First Street, Suite 200, San Jose, CA 95134.

#### **Trademark Acknowledgments**

ARCangel, ARChitect, ARCompact, ARCtangent, High C/C++, High C++, the MQX Embedded logo, RTCS, and VRaptor, are trademarks of ARC International. ARC, the ARC logo, High C, MetaWare, MQX, MQX Embedded and VTOC are registered under ARC International. All other trademarks are the property of their respective owners.

5117-014 April-2008

### **Contents**

| Chapter 1 — Introduction                                      | 9  |

|---------------------------------------------------------------|----|

| Overview of Interfaces                                        | 10 |

| Block Diagram                                                 | 11 |

| Signal Lists                                                  | 11 |

|                                                               |    |

| Chapter 2 — JTAG (Joint Test Action Group)                    |    |

| Communication Module                                          | 13 |

| JTAG Interface                                                | 14 |

| JTAG Signal List                                              | 15 |

| JTAG Pin Connector                                            | 15 |

| JTAG Programmer's Model                                       | 16 |

| The Instruction Register                                      | 17 |

| The JTAG Status Register (Instruction Code 0x8)               | 18 |

| The Transaction Command Register (Instruction Code 0x9)       | 18 |

| The Address Register (Instruction Code 0xA)                   | 19 |

| The Data Register (Instruction Code 0xB)                      | 19 |

| The IDCODE register (instruction code 0xC)                    | 19 |

| The Bypass Register (Instruction Code 0xF)                    | 20 |

| The Boundary Scan Register (Instruction Code 0x0 and 0x1)     | 20 |

| JTAG Port                                                     | 21 |

| The TAP Controller                                            | 21 |

| The TAP Controller State Machine                              | 22 |

| The Debug Port                                                | 24 |

| The Host Interface to BVCI Target                             | 24 |

| Setting Up Read/Write Transactions                            | 25 |

| Setting up a Write Access to the ARC 700 Processor or Memory  | 25 |

| Accessing the Status Register                                 | 26 |

| Setting up a Read Access from the ARC 700 Processor or Memory | 27 |

| JTAG Port Reset                                               | 27 |

| PC - JTAG Communications                                      | 28 |

| Chapter 3 — Bus Bridge                                        | 30 |

| Bus Bridge Block Diagram                                      | 31 |

| BVCI Protocol                                                 | 31 |

|                                                               | 31 |

| BVCI Signal List                                              |    |

| Bus Bridge Block Diagram                                      | 33 |

| Clock Synchronization Unit                                    | 33 |

| Toggle Unit                                                    | 34             |

|----------------------------------------------------------------|----------------|

| Edge Detection                                                 | 34             |

| Phase Detection                                                | 34             |

| Mask Generator                                                 | 35             |

| Last Phase Detect                                              | 35             |

| Clock Crossing BVCI Bridge                                     | 37             |

| Chapter 4 — Bus Interfaces                                     | 38             |

| Instruction Cache (MWIC) to Memory Bus System (via Bus Bridge) | 39             |

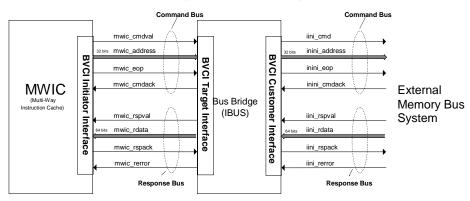

| MWIC and Bus Bridge Block Diagram                              | 39             |

| MWIC to Bus Bridge Signal List                                 | 39             |

| MWIC Bus Bridge to External Bus System Signal List             | 40             |

| MWIC Unimplemented Signal List                                 | 40             |

| Big-Endian Configuration                                       | 41             |

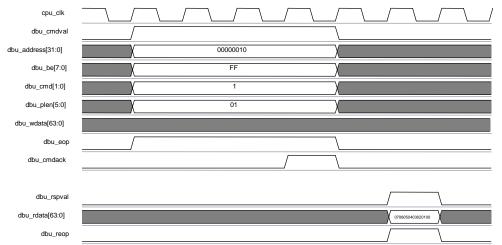

| Interface Timing                                               | 41             |

| DMP to Memory Bus System (via Bus Bridge)                      | 42             |

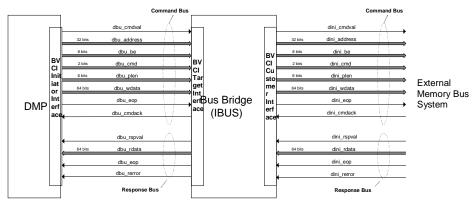

| DMP and Bus Bridge Block Diagram                               | 42             |

| DMP to Bus Bridge Signal List                                  | 42             |

| DMP Bus Bridge to External Bus Signal List                     | 43             |

| DMP Unimplemented Signal List                                  | 44             |

| Big-Endian Configuration                                       | 44             |

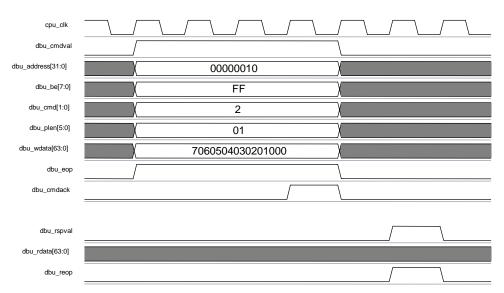

| Interface Timing                                               | 44             |

| Chapter 5 — Closely Coupled Memories (CCM)                     | 49             |

| Closely Coupled Memories                                       | 49             |

| CCM DMI Interfaces                                             | 49             |

| CCM DMI Signal List                                            | 50             |

| Interface Reset State                                          | 51             |

| CCM DMI Behavior                                               | 51             |

| Chapter 6 — XY Memory                                          | 56             |

| XY Memory                                                      | 57             |

| XY DMI interface                                               | 57             |

| XY DMI Signal List                                             | 57             |

| Interface Reset State                                          | 58             |

| XY DMI Behavior                                                | 58             |

| Chapter 7 — Processor Signals                                  | 63             |

|                                                                |                |

| Processor Control Interface                                    | 63             |

| Processor Control Interface<br>Processor Signal List           | 63<br>63       |

| Processor Signal List                                          | 63             |

|                                                                |                |

| Processor Signal List<br>Clocks                                | 63<br>63       |

| Processor Signal List<br>Clocks<br>Reset                       | 63<br>63<br>64 |

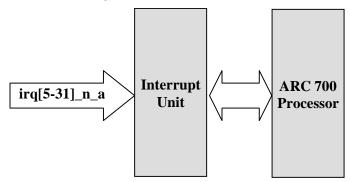

| Feature List                      | 65 |

|-----------------------------------|----|

| Interrupt Signal List             | 65 |

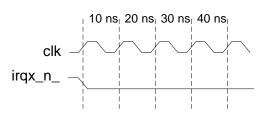

| Incoming Request Interface Timing | 65 |

| Test                              | 66 |

| Test Signal List                  | 66 |

| Figure 1 Example External Bus System Architecture11                                         |

|---------------------------------------------------------------------------------------------|

| Figure 2 The JTAG Communications Module15                                                   |

| Figure 3 Recommended JTAG Pin Connector, Top View16                                         |

| Figure 4 Data Registers Access via the Instruction Register17                               |

| Figure 5 A JTAG Port with an ARC 700 Processor21                                            |

| Figure 6 Internal Structure of the JTAG Port22                                              |

| Figure 7 TAP Controller State Diagram                                                       |

| Figure 8 Loading Data into the Shift Register                                               |

| Figure 9 Internal Structure of the Host Interface to BVCI Target Module                     |

| Figure 10 Loading the Instruction Register                                                  |

| Figure 11 Loading the Data Register26                                                       |

| Figure 12 Loading the Instruction Register (Select Address Register)27                      |

| Figure 13 Example of a Typical ARC 700 System                                               |

| Figure 14 Bus Bridge Structure (IBUS)                                                       |

| Figure 15 Design of the CKSYN                                                               |

| Figure 16 CKSYN Timing Diagram at 4:1 Clock Ratio35                                         |

| Figure 17 CKSYN Timing Diagram at 3:1 Clock Ratio35                                         |

| Figure 18 CKSYN Timing Diagram at 2:1 Clock Ratio                                           |

| Figure 19 CKSYN Timing Diagram at 1:1 Clock Ratio                                           |

| Figure 20 Design of the CBRI - Resets Not Shown                                             |

| Figure 21 Instruction Cache to IBUS                                                         |

| Figure 22 MWIC Target Interface Read Access41                                               |

| Figure 23 DMP to IBUS Interface                                                             |

| Figure 24 Single Cell Packet Read Access45                                                  |

| Figure 25 Single Cell Packet Write Access on BVCI Target Interface between DMP and IBUS     |

| Figure 26 Burst of 4 Cell Packet Read Access on BVCI Target Interface between DMP and IBUS  |

| Figure 27 Burst of 4 Cell Packet Write Access on BVCI Target Interface between DMP and IBUS |

| Figure 28 Locked Read Access followed by Single Write Access on BVCI Target Interface<br>between DMP and IBUS |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| Figure 29 ICCM and DCCM Configuration Example                                                                 | 49  |

| Figure 30 Read Burst on the CCM Burst Interface                                                               | 52  |

| Figure 31 Single Cell Read Operation on the CCM DMI                                                           | 53  |

| Figure 32 Write Burst Operation to the CCM DMI                                                                | 54  |

| Figure 33 Single Cell Write Operation on the CCM DMI                                                          | 55  |

| Figure 34 Read Burst Access on XY Memory DMI.                                                                 | 59  |

| Figure 35 Single Read Access on XY Memory DMI                                                                 | 60  |

| Figure 36 Burst Write Access on XY DMI                                                                        | 61  |

| Figure 37 Single Write Access on XY DMI                                                                       | 62  |

| Figure 38 Interrupt Interface                                                                                 | 64  |

| Figure 39 Example Level Type Interrupt                                                                        | 65  |

| Figure 40 Example Pulse Type Interrupt                                                                        | .66 |

| Table 1 JTAG Signal List                                                                             | 15           |

|------------------------------------------------------------------------------------------------------|--------------|

| Table 2 JTAG Pin Connector Descriptions                                                              | 16           |

| Table 3 JTAG Registers                                                                               | 16           |

| Table 4 JTAG Read/Write Transactions                                                                 | 18           |

| Table 5 Instructions that Employ the Boundary Scan Register                                          | 20           |

| Table 6 Non Implemented Instructions                                                                 | 21           |

| Table 7 JTAG Port Signals                                                                            | 28           |

| Table 8 BVCI Signal List                                                                             | 32           |

| Table 9 MWIC to IBUS Interface                                                                       | 39           |

| Table 10 Bus Bridge to External Memory System                                                        | 40           |

| Table 11 Unimplemented BVCI Interface Signals on the MWIC to IBUS Interface or IE<br>External Memory | BUS to<br>40 |

| Table 12 DMP to IBUS Interface                                                                       | 42           |

| Table 13 Bus Bridge to Memory Bus System                                                             | 43           |

| Table 14 Unimplemented BVCI Interface Signals                                                        | 44           |

| Table 15 DCCM Direct Memory Interface (DMI)                                                          | 50           |

| Table 16 XY DMI Interface Signals                                                                    | 57           |

| Table 17 Processor Control Signal List                                                               | 63           |

| Table 18 Configurable Interrupt Lines                                                                | 65           |

| Table 19 Test Signal List                                                                            | 66           |

# Chapter 1 — Introduction

An ARC® 700 processor based design supports a number of processor island interfaces. These interfaces encompass memory transactions, host debug access and miscellaneous control. The following sections introduce the interfaces in more detail:

- Overview of Interfaces

- Block Diagram

- Signal Lists

## **Overview of Interfaces**

A given ARC® 700 design offers several processor island interfaces. These interfaces encompass memory transactions, host debug access and miscellaneous control.

Interfacing to the processor is achieved mainly indirectly through the following components.

- JTAG communications module

- Bus Bridge

- Bus Interfaces

- <u>Closely Coupled Memory Direct Memory Interface (DMI)</u>

- <u>XY Memory Direct Memory Interface (DMI)</u>

- <u>Control Signals (Clock, Reset, etc)</u>

- Interrupt Unit

- Memory Management Unit (MMU) as described in the ARC 700 MMU Reference

The processor island is the top-level processor island that should be used for integration into a custom system. For additional information on alternative CPU Island interfaces see *AHB Bus Bridge Reference*, *AXI Bus Bridge Reference*, and *ARC Legacy Bus Bridge Reference*.

For further information on the operation of the processor core see *ARCompact Programmer's Reference*.

For information on the processor module hierarchy see the ARC 700 System Reference.

# **Block Diagram**

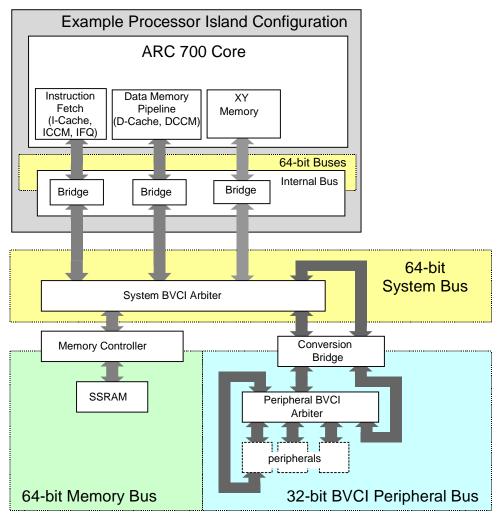

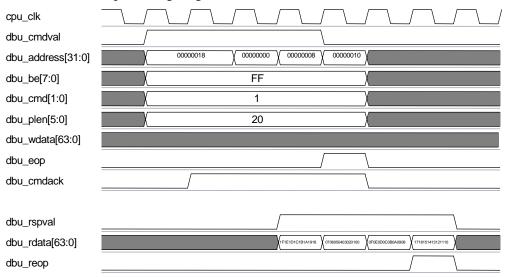

Figure 1 Example External Bus System Architecture

# **Signal Lists**

Various groups of interface signals may appear on the CPU Island. The following signal lists provide more detail on these signal groups:

- JTAG Signal List

- BVCI Signal List

- <u>MWIC Bus Bridge to External Bus System Signal List</u>

- <u>DMP Bus Bridge to External Bus Signal List</u>

- CCM DMI Signal List

- <u>XY DMI Signal List</u>

- Processor Signal List

- Interrupt Signal List

- <u>Test Signal List</u>

# Chapter 2 — JTAG (Joint Test Action Group) Communication Module

The JTAG interface has been introduced as a solution for communicating with the standard ARC 700 and ARCangel systems.

The JTAG module draws its interface and protocol from the IEEE STD 1149.1, providing customers with a standard that is universally recognized. The module contains logic for communicating with the ARC 700 processor and its memory system, providing the host with a high level role where transaction parameters are simply specified.

The following subsections outline principles required in order to communicate with the ARC 700 processor and system memory via the JTAG module:

- JTAG Interface

- JTAG Programmer's Model

- JTAG Port

- <u>Setting Up Read/Write Transactions</u>

- JTAG Port Reset

- <u>PC JTAG Communications</u>

# **JTAG Interface**

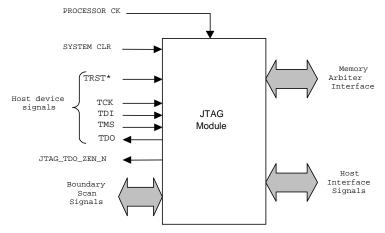

The host device communicates with the JTAG module via four interface signals, these four interface signals are required in order to satisfy the IEEE STD 1149.1 standard. These interface signals provide the host with the ability to control and serially pass data in and out of the module. These signals are shown below:

- TCK Test Clock

- TMS Test Mode Select

- TDI Test Data In

- TDO Test Data Out

An optional JTAG interface signal, Test Reset (TRST\*) has been provided to allow asynchronous initialization of the JTAG port without supplying a clock. Its use is necessary in simulation, but in actual operation it may be tied high. In addition, there is a chip-level signal not specified by the IEEE standard: RTCK. This is a copy of TCK that has been re-driven in the I/O pad ring. If the JTAG emulator chooses to take advantage of it, by using it to clock in TDO, it can compensate for the cable, board, and I/O pad delays to increase the speed at which TCK may be run. This becomes especially important if many chips are chained together on the board.

The module provides various groups of interface signals.

- **The Memory Arbitrator Interface:** The first group interfaces to the memory arbitrator (refer to the *ARC 700 System Components Reference*) and allows the module to access system memory.

- **ARC 700 Host Interface:** The second group drives the ARC 700 host interface bus, providing essential access to the ARC 700 processor's internal register space.

- **Boundary Scan interface:** The third group of signals have been provided in order to allow the inclusion of a Boundary Scan Register. Refer to <u>The Boundary Scan Register (Instruction Code</u> <u>0x0 and 0x1)</u> for a detailed explanation. While this capability remains, the ARC 700 JTAG port has been designed to allow on-chip chaining with other TAP controllers. It may provide an easier integration with ATPG flow to use the TAP controller produced by the ATPG software, and chain it with that of the ARC 700.

- Miscellaneous signals: The final group of signals are provided for system control:

- A processor clock signal is provided allowing the module to carry out read and write transactions to the devices that are synchronized to the <u>processor clock</u>. The JTAG clock, TCK, is designed to run at maximum frequency is 50% of the processor clock. In RTL simulation the ratio of <u>system clock</u> to processor clock may affect the maximum frequency of TCK. In silicon there are additional timing constraints, for example the time from the transition on the input JTAG clock to the output of JTAG TDO must be allowed for.

- A system clear signal is included allowing the module to be reset asynchronously with all devices in the system.

- An output enable signal, jtag\_tdo\_zen\_n, is provided allowing the output TDO to go high impedance when inactive. Tri-state is provided for the case of parallel connection of the other driving circuitry to TDO. Should TDO not be connected to any other driving circuitry, the tri-state output need not be implemented.

— The JTAG busy signal, jtag\_busy, can be used to provide a helpful indication that there is activity on the debug channel, for example to drive an LED on a development board. If not required, this signal can be left open.

Figure 2 illustrates the signals that make up the JTAG module.

Figure 2 The JTAG Communications Module

The TMS input interface signal should be connected to a pull up component as part of the IEEE STD 1149.1 requirement, thus allowing the module to be reset if the input to TMS is undefined (for example high impedance) and TCK is applied. Pull-ups are not required for TDI, TDO or TCK. The reset mechanism is described in <u>The TAP Controller State Machine</u>.

### **JTAG Signal List**

The following JTAG interface signals may appear on the CPU Island:

| Signal         | Direction | Description                   |

|----------------|-----------|-------------------------------|

| jtag_tdi       | Input     | JTAG data input               |

| jtag_tms       | Input     | JTAG mode select              |

| jtag_tck       | Input     | JTAG clock                    |

| jtag_trst_n    | Input     | JTAG reset                    |

| jtag_tdo       | Output    | JTAG data output              |

| jtag_tdo_zen_n | Output    | JTAG TDO output enable signal |

| jtag_rtck      | Output    | JTAG re-timed clock           |

| jtag_busy      | Output    | JTAG busy signal              |

#### Table 1 JTAG Signal List

#### JTAG Pin Connector

This is the recommended board connector to attach a debug emulator to the JTAG signals on the board. It is a 20-pin IDC connector, with pins on 0.100" centers, keyed and shrouded.

| VTref        | 1 ●        | • 2 | Vsupply |

|--------------|------------|-----|---------|

| TRST*        | 3 🔴        | • 4 | GND     |

| TDI          | 5 🔴        | • 6 | GND     |

| TMS          | ר ⊢        | • 8 | GND     |

| тск          | 9 🔴        | •10 | GND     |

| RTCK         | 11 ●       | •12 | GND     |

| TDO          | 4 13●      | •14 | GND     |

| (leave open) | 15 \bullet | •16 | GND     |

| (leave open) | 17 ●       | •18 | GND     |

| (leave open) | 19 🔴       | •20 | GND     |

|              |            |     |         |

Figure 3 Recommended JTAG Pin Connector, Top View

Table 2 JTAG Pin Connector Descriptions

| Signal  | Description and Notes                                                                                                                     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК     | Clock input to debug port. Must be pulled to defined state on board for so as not to clock circuitry when no debug emulator is connected. |

| RTCK    | Clock output. If not implemented on chip, drive from TCK on board.                                                                        |

| TMS     | Test Mode Select input. Must be pulled up on board.                                                                                       |

| TDI     | Test Data In input. Must be pulled up on board.                                                                                           |

| TDO     | Test Data Out output. Must be pulled up on board.                                                                                         |

| TRST*   | Test Reset. Must be pulled up on board.                                                                                                   |

| VTref   | Target Reference Voltage. Should be tied to Vdd of chip.                                                                                  |

| Vsupply | Supply voltage for emulator pod. Should be tied to Vdd of chip.                                                                           |

| GND     | Ground. Tie to Vss of chip.                                                                                                               |

While it is not necessary, the speed of the JTAG debug connection can be maximized if TDO and RTCK use drivers capable of driving 50-Ohm transmission lines.

## **JTAG Programmer's Model**

The JTAG module includes eight internal registers as shown in Table 3. The host can define a read or write transaction to a memory location or an ARC 700 register through some of these internal registers. Six of the eight registers are collectively referred to as data registers (IEEE STD 1149.1). The remaining registers are the instruction register, which is central in the role of accessing all data registers and the Boundary Scan register.

| Value   | Code      | JTAG Register                | ТҮРЕ        |  |

|---------|-----------|------------------------------|-------------|--|

| N/A     | N/A       | INSTRUCTION REGISTER*        | Instruction |  |

| 0x8     | 1000      | JTAG STATUS REGISTER         | Data        |  |

| 0x9     | 1001      | TRANSACTION COMMAND REGISTER | Data        |  |

| 0xA     | 1010      | ADDRESS REGISTER             | Data        |  |

| 0xB     | 1011      | DATA REGISTER                | Data        |  |

| 0xC     | 1100      | IDCODE REGISTER              | Data        |  |

| 0xF     | 1111      | BYPASS REGISTER*             | Data        |  |

| 0x0/0x1 | 0000/0001 | BOUNDARY SCAN REGISTER*      | BSR         |  |

|         |           |                              |             |  |

| - Bisters and |             |

|---------------|-------------|

| Table 3 JTA   | G Registers |

**NOTE** \* Required as part of IEEE STD 1149.1 specification.

Each of the registers are described in the following sections:

- <u>The Instruction Register</u>

- The JTAG Status Register (Instruction Code 0x8)

- The Transaction Command Register (Instruction Code 0x9)

- <u>The Address Register (Instruction Code 0xA)</u>

- The Data Register (Instruction Code 0xB)

- <u>The IDCODE register (instruction code 0xC)</u>

- The Bypass Register (Instruction Code 0xF)

- The Boundary Scan Register (Instruction Code 0x0 and 0x1)

#### The Instruction Register

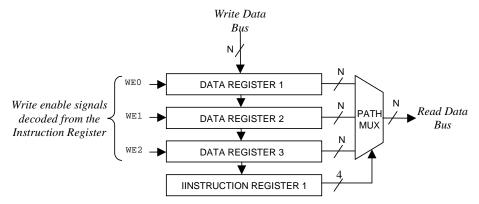

The Instruction register is used to gain access to all data registers. Each data register is addressed by a unique 4-bit instruction code.

| 31       | 4 | 3  | 2    | 1   | 0  |

|----------|---|----|------|-----|----|

| Reserved |   | In | st ( | Cod | le |

In order to access the required data register, the correct code should be written into the instruction register. Figure 4 illustrates the relationship between the instruction and data registers. The instruction shift register is loaded with 0x1 in Capture-IR, so that external circuitry, by looking for a transition when in Shift-IR, can detect a stuck-at fault in the JTAG chain.

**NOTE** Because of this behavior, which is specified in IEEE 1149.1, the current contents of the instruction register can not be read by the external circuitry. The register itself is initialized to point to the IDCODE register in Test-Logic-Reset.

#### Figure 4 Data Registers Access via the Instruction Register

In addition to accessing the data registers (refer to subsections <u>The JTAG Status Register (Instruction</u> <u>Code 0x8)</u> to <u>The Bypass Register (Instruction Code 0xF)</u>), the instruction register is also used to select a test sequence that should be applied to the device. These test sequences use a special data register known as the Boundary Scan Register (refer to <u>The Boundary Scan Register (Instruction</u> <u>Code 0x0 and 0x1)</u>).

### The JTAG Status Register (Instruction Code 0x8)

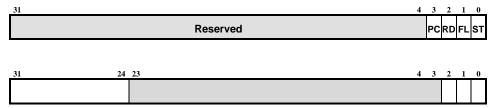

The JTAG Status Register is read only and is used by the host device to obtain important information on the state of the JTAG module or the result of an ARC 700 processor or memory access. The bits of the register are assigned as follows.

Each field in the JTAG Status register reflects the following information:

- Bit 0 Stalled (ST) flag indicates that the current transaction has stalled. This flag is set when the ARC 700 processor asserts the hold\_host signal to lengthen the duration of a read or write transaction.

- Bit 1 Failure (FL) flag indicates that a read (or write) has failed when it is true. For example, this flag would be set if an access to a core register is attempted when the processor is running. The failure flag is cleared automatically when a new transaction is started.

- Bit 2 Ready (RD) flag indicates whether the JTAG module is available to accept another transaction command. This flag is set when a transaction has just completed or when the JTAG module is idle.

- Bit 3 PC\_SEL (PC) flag, is set to the value that is assigned to the AUX\_PCPORT auxiliary register (refer to the Extension Functions section in the *ARCangel development board manual*). For example, this flag would be set if 1 was written to the AUX\_PCPORT auxiliary register, and cleared if 0 was written to AUX\_PCPORT.

- Bits 31 down to 24 Reserved.

### The Transaction Command Register (Instruction Code 0x9)

The Transaction Command Register is used to specify the communication transaction that should be performed.

The JTAG module supports eight different accesses or transactions, which are shown in Table 4 with their associated encoding.

| Value | Alue Code Communication Transaction |                                                |

|-------|-------------------------------------|------------------------------------------------|

| 0x0   | 0000                                | Write to a memory location                     |

| 0x1   | 0001                                | Write to a ARC 700 core register               |

| 0x2   | 0010                                | Write to a ARC 700 auxiliary register          |

| 0x3   | 0011                                | NOP, The register is initialized to this value |

| 0x4   | 0100                                | Read from a memory location                    |

| 0x5   | 0101                                | Read from a ARC 700 core register              |

| 0x6   | 0110                                | Read from a ARC 700 auxiliary register         |

Table 4 JTAG Read/Write Transactions

| Value | Code | Communication Transaction  |

|-------|------|----------------------------|

| 0x7   | 0111 | Write to a MADI* register  |

| 0x8   | 1111 | Read from a MADI* register |

**NOTE** The MADI register is only available where the debugging of multiple ARC 700 processor systems is required. The MADI system is no longer the recommended way of debugging multiple cores on a chip. ARC now recommends that each processor have its own JTAG port, and that these be chained together by distributing TCK, TMS, and TRST\* in parallel, and connecting the TDO from one processor to the TDI of the next.

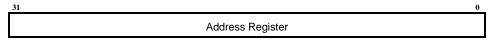

### The Address Register (Instruction Code 0xA)

The Address Register is used to supply the address for read and write transactions to the ARC 700 registers and system memory.

Address Register Accesses to memory must always be given in bytes. Access to the ARC 700 internal registers is

specified by their register numbers. The value contained in this register is automatically incremented by four (a memory access) or one (an ARC 700 register access) when a read or write transaction has completed. This feature is used to save valuable cycle time when downloading / uploading a stream of data, hence the register does not need to be rewritten with the next address value.

### The Data Register (Instruction Code 0xB)

The data register performs two functions. When data is written to this register, it is placed into a write buffer that drives two write data buses, one for the ARC 700 host interface and other for the memory arbitrator interface. The bus is used to specify the data contents that should be written when performing a write transaction.

When reading this register a read buffer is selected. The read buffer is used to store data retrieved from the target device during a read transaction. The appropriate read data bus (arbitrator or host interface) is selected according to which device the host is accessing.

### The IDCODE register (instruction code 0xC)

The IDCODE register is used by the JTAG emulator to identify the core as an ARC 700 core.

| _ | 31 | 30 | 29         | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7  | 6   | 5    | 4   | 3    | 2    | 1   | 0 |

|---|----|----|------------|----|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|-----|------|-----|------|------|-----|---|

|   |    |    | AG<br>sior |    |    |    | ,  | AR | CN | lum | nbe | r  |    |    |    | AI | RC | Ту | ce |    | AR | C. | JEC | DEC | СМ | anı | ufac | tur | er's | s Co | ode | 1 |

Each field in the IDCODE register reflects the following information:

- Bits 31 down to 28 These bits define the version of the JTAG module. Currently set to the value 0x1.

- Bits 27 down to 18 This field will be set by the designer to the number of ARC processors swithin the system. It will have the same value as the corresponding field in the IDENTITY register in auxiliary space, if there are fewer than 256 ARC processors in the system.

- Bits 17 down to 12 This field will be set to 0x03 to identify the processor type as an ARC 700 type.

- Bits 11 down to 1 This field contains the code assigned to ARC International by JEDEC, encoded as specified in the IEEE 1149.1-2001 standard. ARC has been assigned the manufacturer's code 0x58 in group five, so this field encodes to 0100 101 1000.

- Bit 0 This field is fixed at 1, as specified in the IEEE 1149.1-2001 standard. This is used, along with the previous field, to allow automatic discovery when the chain is initialized. JEDEC will never assign the manufacturer's code 0x7F in group 0. The JTAG emulator, therefore, can shift the 32-bit IDCODE 0x000000FF into TDI at the beginning of the chain after reset. The standard specifies that upon receiving a TCK when in the Reset-Test-Logic state, the instruction register will be initialized to point to the IDCODE register if it exists, and to the BYPASS register otherwise. In Capture-DR, the shift register is loaded with this 32-bit code if IDCODE is in the instruction register, and with a single bit of 0 if BYPASS is. Thus the external circuitry can examine TDO in Shift-DR, and know if it's zero that this TAP controller has only a 1-bit bypass register, and if it's one that this TAP controller has a 32-bit IDCODE register. By shifting through looking for these until the 0x000000FF appears, the emulator can uniquely identify the number and kind of devices in the chain.

### The Bypass Register (Instruction Code 0xF)

The Bypass Register is required as part of the IEEE STD 1149.1 standard.

| _31      | 1 0 |

|----------|-----|

| Reserved | BP  |

|          |     |

When this register is selected, the serial data input (TDI) is connected to the serial data output (TDO) through this register. The data on TDI is passed to TDO on the rising edge of the JTAG clock TCK when in Shift-DR, and the register is initialized to 0 in Capture-DR. In all other states, the data in this register is held.. The Bypass register is automatically selected when a reset is applied to the JTAG module allowing the data on TDI to bypass the core logic to TDO.

### The Boundary Scan Register (Instruction Code 0x0 and 0x1)

The Boundary Scan register is selected when the four-bit code 0000 or 0001 is written into the Instruction register. This register is used to retrieve the logic state of a device and control data on its input and output pins. The register does not exist within the module and must be provided externally (it is connected to the JTAG module via the boundary scan interface). The codes 0000 and 0001 relate to the EXTEST and SAMPLE/PRELOAD instructions as shown in Table 5. These boundary scan instructions are necessary as part of the IEEE STD 1149.1. Refer to the Application Note 'Interfacing the JTAG Module to a Boundary Scan Register' for more detail.

**NOTE** Since the ARC 700 TAP controller may be chained on the chip with other TAP controllers, use of a separate TAP controller known to be compatible with the user's test software is recommended.

| Value | Code | Instruction    |

|-------|------|----------------|

| 0x0   | 0000 | EXTEST         |

| 0x1   | 0001 | SAMPLE/PRELOAD |

Table 5 Instructions that Employ the Boundary Scan Register

The instructions contained in Table 6 have also been defined in the IEEE STD 1149.1. These are optional instructions and are not supported with version 1.0 of the JTAG module.

| Instruction | Description                                                         |  |  |  |  |

|-------------|---------------------------------------------------------------------|--|--|--|--|

| INTEST      | Performs an internal test (uses the boundary scan register)         |  |  |  |  |

| RUNBIST     | Runs an internal core logic test (additional logic)                 |  |  |  |  |

| USERCODE    | Captures user defined information about a device (additional logic) |  |  |  |  |

#### Table 6 Non Implemented Instructions

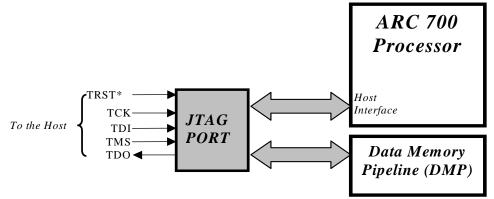

# JTAG Port

The block diagram shown in Figure 5 shows how the JTAG communications port integrates within an ARC 700 system. It is linked to the host interface of the ARC 700 processor in addition to system memory via the Data Memory Pipeline (DMP).

Figure 5 A JTAG Port with an ARC 700 Processor

- <u>The TAP Controller</u>

- <u>The TAP Controller State Machine</u>

- <u>The Debug Port</u>

- The Host Interface to BVCI Target

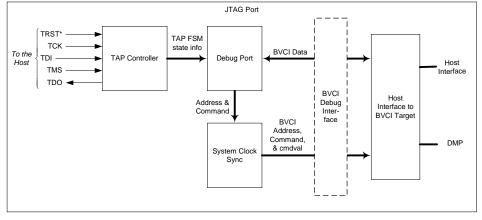

#### The TAP Controller

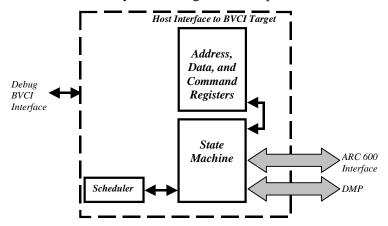

The Test Access Port (TAP) controller is central to the operation of the JTAG module as shown in Figure 6. All internal register accesses are performed serially using the TAP controller. An accompanying block, the Debug Port, serves as the workhorse, performs the majority of internal (accessing internal JTAG registers) and external (performing BVCI transactions) tasks. The Debug Port and the TAP Controller are clocked off of TCK, and a separate module synchronizes the BVCI initiator signals to the system clock. On the other side of the BVCI Debug Interface, there is a module that contains the address, data, command, and status registers, and handles the host interface and DMP transactions: the Host Interface to BVCI Target module. This allows the user, if desired, to replace the JTAG port, either by a custom interface to an external debugger, or to another processor in a master/slave configuration.

Figure 6 Internal Structure of the JTAG Port

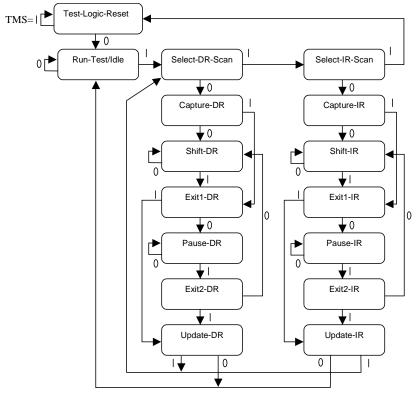

The TAP controller is an internal state machine that is controlled entirely by the host using the TMS and TCK interface signals. The controller is used to indirectly initiate communication transactions and access the internal JTAG registers. The state machine consists of 16 states that are connected together as shown in Figure 7.

#### The TAP Controller State Machine

#### Figure 7 TAP Controller State Diagram

Each state contains at least one entry point with two possible exit paths. A state transition is performed on the rising edge of TCK. The decision to determine the exit path is made according to the logic level of TMS.

The Test-Logic-Reset state is used to initialize all internal JTAG registers and control signals to default contents and inactive logic levels respectively. The state is entered immediately when TRST\* is asserted. In addition, this state can also be entered (regardless of the current state) at any time during operation by holding TMS high and applying a maximum of five clock pulses on TCK.

The Run-Test/Idle state always precedes the Test-Logic-Reset, Update-DR and Update-IR states on the rising edge of TCK when TMS is low. This state is employed to initiate a read/write access or place the JTAG module in the idle state. The read/write access defined by the address, data and command registers only occurs once on entry to Run-Test/Idle.

The remaining section of the state diagram (in Figure 7) contains two state sequence structures that are used to access all internal JTAG registers. Registers can be written to or read from serially using the TDI and TDO signals along with the aforementioned TCK and TMS signals. Both structures are identical, however, as denoted by the mnemonics IR and DR, one structure is used to access the instruction register and the other dedicated solely to accessing all data registers.

An internal JTAG register is accessed by placing the TAP controller into the appropriate scan structure (Select-DR-Scan or Select-IR-Scan). The data contents of the selected register are loaded into a shift register in the Capture-xR state. The state is then entered from the Select-xR-Scan state by pulling TMS low and applying a clock pulse on TCK. Capture occurs when the Capture-xR state is exited.

The shift register is used to shift data into the chain from TDI (write phase) simultaneously shifting data out of the chain at TDO (read phase).

By holding TMS low and applying a second clock pulse on TCK the TAP controller goes into the Shift-xR state. The Tap Controller remains in the Shift-xR state when TMS is held low. This state allows data to be loaded serially (least significant bit first) into the shift register. The TDI signal is always sampled on the rising of edge of TCK, starting on the second entry into the Shift-xR state. The data shifted out is placed on TDO on the falling edge of TCK starting on the first entry into the Shift-xR state. The last sample of TDI is always performed when exiting the Shift-xR state. For instance, when the instruction register contains the BYPASS instruction, a 0 is loaded into the 1-bit bypass register on the clock that exits Capture-DR and enters Shift-DR. At this point, the 0 will appear on TDO. On the next clock, TDI will appear on TDO, and data will continue to be shifted through until the final TDI is shifted to TDO on the clock which exits Shift-DR and enters Exit1-DR.

When the data is finally shifted in or out of the shift register, the selected JTAG register is updated with the shift register contents when the TAP controller is placed into the Update-xR state. Updating occurs on the falling edge of TCK after the state is entered.

The remaining states Pause-xR and Exit2-xR are used to stall the shift process if the data to be shifted in cannot be presented in time for the next rising edge of TCK (assuming a continuous frequency on TCK).

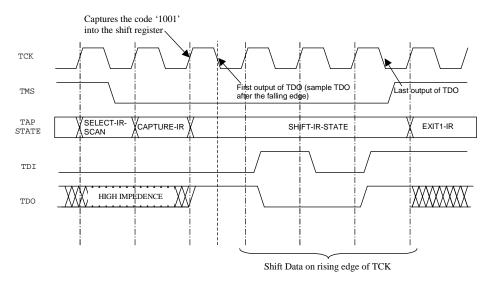

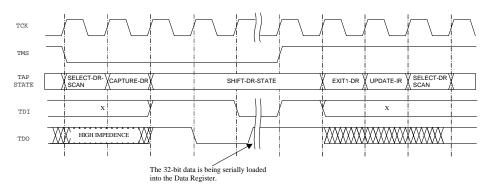

#### Figure 8 Loading Data into the Shift Register

The timing diagram in Figure 8 illustrates the concept of shifting data into the shift register using TCK, TMS & TDI. The diagram illustrates the host device writing to the instruction register with the four-bit value 1010, thus selecting the Address register. In the capture stage the four-bit value 0001 is loaded into the shift register ready to be shifted out. The instruction register is not updated (and the Address register is not selected) with the shift register contents until the Update-IR state is entered. Following the Update-IR state the Select-DR-Scan state structure is entered to access the Address register.

During the Capture-IR phase the four-bit value 0001 is always loaded into the shift register, regardless of the instruction register contents. The first two least significant bits aid in diagnosing faults along the IEEE 1149.1-1990 bus.

### The Debug Port

The debug port module contains all the registers specific to the JTAG interface. This includes the instruction and data shift registers, the instruction register itself, the bypass register, and the IDCODE register. It also contains a restricted BVCI initiator, which, in conjunction with the system clock synchronization module, is responsible for access to the address, data, transaction command, and status registers, and for initiation of read and write accesses. It must be stressed that the debug BVCI interface is completely separate from the memory BVCI interfaces. The address space of the debug BVCI interface contains only six valid addresses in its stock configuration: the addresses of the address, data, transaction command, and status registers, along with two special addresses which, when written with any data, cause the read/write access to be initiated and the address, data, and command registers to be reset, respectively.

### The Host Interface to BVCI Target

The address, data, status, and transaction command registers are to be found in the host interface to BVCI target module (as shown in Figure 9). It contains a state machine, which performs all read and write bus transactions that are supported by the JTAG module. This is providing there is a valid code in the Transaction Command register; an access is initiated by placing the TAP controller into the Run-Test/Idle state, which causes the debug port to write the do\_cmd address on the BVCI interface. This request is then fed to the state machine. The scheduler is responsible for verifying

transaction requests and providing the mechanism that allows the host device and the JTAG module to maintain a strict synchronizing relationship.

Figure 9 Internal Structure of the Host Interface to BVCI Target Module

The scheduler verifies a transaction request from the host device by checking the value contained in the Transaction Command register. The transaction request signal is asserted only when the Transaction Command register contains a valid code and a write to the do\_cmd address occurs on the debug BVCI interface. The scheduler asserts a transaction request signal to start the defined bus transaction. The BVCI target always responds to all commands in a single cycle. It is the responsibility of the debugger to maintain synchronization by polling the status register for the READY bit after an access has been started.

## **Setting Up Read/Write Transactions**

A guide through the stages of defining and initiating read and write accesses:

- Setting up a Write Access to the ARC 700 Processor or Memory

- <u>Accessing the Status Register</u>

- Setting up a Read Access from the ARC 700 Processor or Memory

#### Setting up a Write Access to the ARC 700 Processor or Memory

A write access requires placing the TAP controller into the Test-Logic-Reset state. This should reset the JTAG module. This initializes all the internal JTAG registers to default values and all interface control signals to inactive logic levels. This initialization process is performed by asserting TRST\* or by holding TMS high and applying a maximum of five clock pulses on TCK. This will ensure that when the Run-Test/Idle state is entered a bus transaction is not triggered from a valid code already contained in the Transaction Command register.

The reset procedure is not required for every read and write access, and is performed only when there has been a system reset. The next stage is to set-up the transaction parameter registers. These include the Address register, Data register and the Transaction Command register.

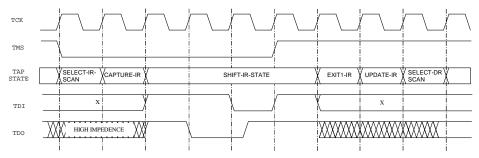

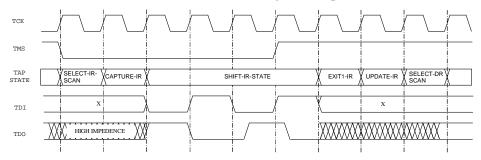

The contents of the Address and Data registers are loaded with the appropriate values so that the write access can be performed on the ARC 700 processor or to memory. Firstly, the instruction register is loaded with the code for accessing the Data register. This is accomplished by entering the Select-IR-Scan state and updating the Instruction register. Then the code 1011 for the Data register is

serially loaded in the SHIFT-IR state. The timing diagram for writing the instruction register with the code 1011 which selects the Data register is shown in Figure 10.

Figure 10 Loading the Instruction Register

X = Don't care, Z = high impedance

The Select-DR-Scan state is then selected to serially load in the data to be employed by the write data bus when write access is performed. This is shown in the timing diagram in Figure 11.

Figure 11 Loading the Data Register

The Address register is now accessed by loading the code 1010 into the instruction register. We then enter the Select-DR-Scan state structure and serially load in the data to be used on the address bus.

The last stage involves writing the Transaction Command register with the code instructing the JTAG module to perform a write transaction to either the memory or the ARC 700 registers.

Once all the transaction parameters have been setup, the write transaction is started by placing the TAP controller into the Run-Test/Idle state.

To obtain information about the transaction, the JTAG Status register is accessed. Since this is a read only register the signal supplied on TDI is ignored when the register contents are shifted out through TDO. The appropriate bit fields are then checked to verify a write transaction was performed.

### Accessing the Status Register

The JTAG Status register is accessed in the following way, the first bit in the Status register (refer to The JTAG Status Register (Instruction Code 0x8)) is shifted out to determine whether the JTAG module has been stalled. If the stalled bit is set, then the Select-DR-Scan state structure is exited and returned to later. This happens if a requested transaction is already underway.

If the JTAG module is not stalled, then the second bit is shifted out of the Status register to determine whether that transaction has failed. If the failed bit is set then the Select-DR-Scan state structure is exited.

If the failed bit is not set then the ready bit is shifted out to determine whether the transaction has completed or not. If the ready bit is set, then the transaction has finished and a new transaction can be started. If it has not been set, then the Select-DR-Scan state structure is exited and the above procedure is repeated.

The PC\_SEL is an optional bit that does not need to be shifted out.

### Setting up a Read Access from the ARC 700 Processor or Memory

Setting up a read transaction follows almost the same procedure as setting up a write transaction.

The Address register is accessed by writing the 4 bit code 1010 into the instruction register. Select-IR-Scan state structure is selected and the code 1010 is serially loaded. When the Update-IR state is entered the instruction register is updated and the Address register is selected.

Figure 12 Loading the Instruction Register (Select Address Register)

The data register does not need to be accessed at this stage as a read transaction is being performed.

The last stage of setting up the transaction parameter registers involves writing to the Transaction Command register with the required read transaction.

When all the transaction parameters have been set up the access is started by placing the TAP controller into the Run-Test/Idle state.

To obtain information about the transaction, the JTAG status register is interrogated. Since this is a read only register the signal supplied on TDI is ignored when the register contents are shifted out through TDO. The appropriate bit fields are then checked to verify the read transaction. Refer to <u>Accessing the Status Register</u> for a standard routine on how to decode the JTAG Status register.

When the transaction has completed successfully the data register is selected. Select-IR-Scan state structure is selected and the code 1011 is serially loaded into the instruction register. The Select-DR-Scan state is then entered and data is shifted out from the selected device.

## **JTAG Port Reset**

When implementing a system with a JTAG port, pin SS1 must be connected to logic on the board such that, when the PC sets signal SS1 low (active), signal xclr will be driven low to reset the ARC 700 processor.

# **PC - JTAG Communications**

The ARCangel3 (AA3) Development board features an interface to a bi-directional PS/2 parallel port. This port allows the following functions to be performed:

- start, stop and single step the ARC 700 processor

- read/write all core registers

- read/write all auxiliary registers

- read/write external memory

- perform system reset

- generate a ARC 700 interrupt

With the exception of resets, all functions are performed by downloading a 32-bit address/control word, followed by 32 bits of send or receive data. The 32 bit values are sent serially, least significant bit first.

Table 7 shows a summary of the signals in use on the parallel port connector.

| Pin | Driver | Signal | Function                                                                         |

|-----|--------|--------|----------------------------------------------------------------------------------|

| 1   | pc     | TCK    | Test Clock - Used to control data flow. Data from the PC latched on rising edge. |

| 2   |        |        | Not used                                                                         |

| 3   |        |        |                                                                                  |

| 4   |        |        |                                                                                  |

| 5   |        |        |                                                                                  |

| 6   |        |        |                                                                                  |

| 7   |        |        |                                                                                  |

| 8   | pc     | TMS    | Test Mode Select – used to select the TAP controller states                      |

| 9   | pc     | TDI    | Test Data In - Serial Data input                                                 |

| 10  |        |        | Not used                                                                         |

| 11  | aa     | busy   | Valid for AA3.                                                                   |

|     |        |        | Set high whenever AA3 JTAG port is in non-idle state.                            |

|     |        |        | Drives the right-hand LED on AA3.                                                |

| 12  |        |        | Not used                                                                         |

| 13  | aa     | TDO    | Test Data Out – serial data out                                                  |

| 14  |        |        | Not used                                                                         |

| 15  |        |        | Not connected                                                                    |

| 16  | pc     | ss0    | Valid for AA3. See following page.                                               |

| 17  | pc     | ss1    | Valid for AA3. See following page.                                               |

| 18  |        | 0v     |                                                                                  |

| 19  |        | 0v     |                                                                                  |

#### Table 7 JTAG Port Signals

| Pin | Driver | Signal | Function |

|-----|--------|--------|----------|

| 20  |        | 0v     |          |

| 21  |        | 0v     |          |

| 22  |        | 0v     |          |

| 23  |        | 0v     |          |

| 24  |        | 0v     |          |

| 25  |        | 0v     |          |

As a requirement for the SeeCode DLL an external reset signal should be provided in the JTAG interface version of the ARC 700 processor allowing the chip to be reset. There is a soft reset mechanism in the JTAG module that is used to reset JTAG module alone.

ss0 and ss1 are used as follows when a JTAG comms port is implemented on the AA3 development board. At the D25 connector to the AA3 board, the functionality of ss0 and ss1 is:

| s1 |

|----|

|    |

| 0 | 0 | Reset the ARC 700 system on the FPGA |

|---|---|--------------------------------------|

| 1 | 0 | FPGA Configuration download          |

| 0 | 1 | ARC 700 system in normal operation   |

| 1 | 1 | ARC 700 system in normal             |

# Chapter 3 — Bus Bridge

A bus bridge provides several useful architectural functions. The bridge provided performs the following functions.

- Bus protocol translation

- Bus timing registering

- Clock crossing

Bus protocol translation enables the ARC 700 design to interface to any bus topology that uses a specific bus protocol. The ARC 700 processor uses native BVCI (mandatory signaling subset as defined by pages 27, and 29 - 30 of the VSI Alliance Virtual Component Interface Standard Version 2 (OCB 2 2.0)). In order to interface to a non-BVCI memory system, an appropriate bus bridge is needed that can perform BVCI to non-BVCI bus protocol standards conversion. The default bridge that is included in an ARC 700 processor build performs no bus protocol translation, therefore the default memory interfacing standard it BVCI.

Bus timing isolation is used to register signals that are late arriving (relative to the rising edge of the CPU clock) from the various processor components, such as the instruction and data caches. The output of the bridge interface ensures that a transaction starts on the rising edge of the clock, providing a complete cycle for any proprietary memory subsystem.

Clock crossing provides the ability to support a different clock speed on the system bus to that of the processor internal bus (BVCI).

The following sections describe the bus bridges in more detail:

- Bus Bridge Block Diagram

- BVCI Protocol

- Bus Bridge Block Diagram

- <u>Clock Synchronization Unit</u>

- Clock Crossing BVCI Bridge

For additional information on alternative CPU Island interfaces see AHB Bus Bridge Reference, AXI Bus Bridge Reference, and ARC Legacy Bus Bridge Reference.

### **Bus Bridge Block Diagram**

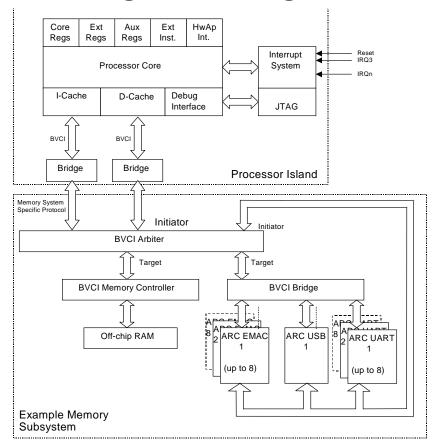

Figure 13 Example of a Typical ARC 700 System

# **BVCI** Protocol

Basic Virtual Component Interface (BVCI), is a sub-set of the Virtual Component Interface (VCI) standard, and it is a protocol standard resulting from the work of the On-Chip Bus Development Working Group of the Virtual Socket Interface Alliance (VISA). This open standard was written to provide a general interface specification for Virtual Components (hardware Intellectual Property) so that they can be easily used to built System-on-Chip (SoC). Designed primarily as a point-to-point on-chip protocol, it is technology independent but has the advantage of being a powerful protocol, and yet inherently efficient and simple to implement. The VCI standard defines three levels of Complexity, and they are, in the order of complexity, Peripheral VCI (PVCI), Basic VCI (BVCI) and Advance VCI (AVCI). PVCI protocol is a sub-set of BVCI and AVCI adds onto BVCI by specifying optional signals that can be added.

The internal processor bus protocol implements BVCI. BVCI defines an inherently split protocol. It allows multiple access commands to be sent from an initiator interface to a target interface before data or responses of the commands are returned. Its flexibility also makes it suitable for most applications, and makes it relatively easier to translate to other protocols.

With the BVCI protocol, individual access commands are sent as cells over a synchronous command bus. The read data and access response are then returned as cells over a separate response bus. These cells are combined to form packets (burst transfers). Handshaking between initiator and target interface at cell level is performed using simple cell valid and acknowledgement signals. One or more cells are packaged into packets, using additional signals to denote the last cell of a packet and define the addressing scheme.

Detailed information on the BVCI protocol may be obtained from:

• VSI Alliance - <u>www.vsi.org</u>: Virtual Component Interface Standard (v2.0 - OCB 2 2.0)

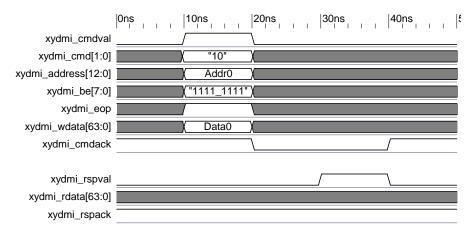

### **BVCI Signal List**

The following BVCI interface signals may appear on the CPU Island, where \* is the particular BVCI signal group:

| Signal          | Direction | Description                                                                                                       |

|-----------------|-----------|-------------------------------------------------------------------------------------------------------------------|

| *_address[31:0] | Output    | <i>Physical Byte Address</i> . It needs to be updated on every cycle during a burst.                              |

| *_be[7:0]       | Output    | <i>Byte Enables</i> . They can be byte, word, long word or double long words sized transactions.                  |

| *_cmd[1:0]      | Output    | Command. The types that can be issued are:                                                                        |

|                 |           | • Read $-0x1$                                                                                                     |

|                 |           | • Write $-0x2$                                                                                                    |

|                 |           | • Locked Read – 0x3                                                                                               |

| *_cmdval        | Output    | <i>Command Cell Validate</i> . The values on the command bus are valid when this signal is true.                  |

| *_eop           | Output    | <i>End of Packet</i> . This signal is asserted on the last burst cycle to indicate the end of that burst request. |

| *_plen[5:0]     | Output    | Packet Length. Describes the packet length in bytes:                                                              |

|                 |           | • Byte $-0x1$                                                                                                     |

|                 |           | • Word (16 bits) $-0x2$                                                                                           |

|                 |           | • Longword (32 bits) – 0x4                                                                                        |

|                 |           | • Burst of 32 bytes (4 cells packet) – 0x20                                                                       |

| *_wdata[63:0]   | Output    | Write Data. This is the data from a write.                                                                        |

| *_cmdack        | Input     | <i>Command Acknowledge</i> . Acknowledges the valid command cell.                                                 |

| *_rdata[63:0]   | Input     | Read Data. This is the returning data from a read request.                                                        |

| *_reop          | Input     | End of packet on the response bus.                                                                                |

| *_rspval        | Input     | Response Valid.                                                                                                   |

| *_rerror        | Input     | <i>Response Error</i> . Bus errors are transferred directly to the ARC 700 core via the BVCI interface.           |

Table 8 BVCI Signal List

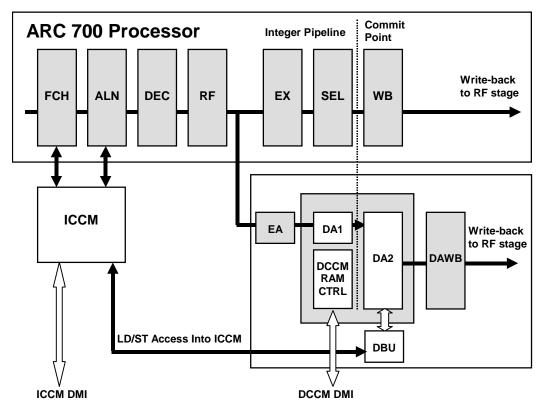

## **Bus Bridge Block Diagram**

#### Figure 14 Bus Bridge Structure (IBUS)

Logic that is contained within the bus bridge is referred to as the *IBUS*. The name *Internal Bus* is derived from the concept of the processor island. A processor island denotes a collection of processor specific components that operate from a single processor clock. Processor Island components natively make use the BVCI protocol; therefore the IBUS protocol is BVCI.

The bridge is made up of two sub-modules and they are:

- Clock Crossing Bridge

- Clock Synchronization Unit

The Clock Crossing Bridge (CBRI) is responsible for converting accesses from a processor island component (such as the instruction cache), which is on the CPU clock domain (clk\_cpu) onto the memory system clock domain (clk\_sys). The supported frequency ratios of clk\_cpu to clk\_sys are 1:1, 2:1, 3:1 and 4:1, and both clocks have to be phased locked and clock tree balanced. This module is also responsible for isolating the timing within the internal bus from that of the memory system bus.

The Clock Synchronization Unit (CKSYN) is responsible for keeping track of the phase relationship between clk\_cpu, used within the processor island, and clk\_sys. This unit sends out synchronization signals to the bridge to help it latch and transfer data correctly.

All modules in the bridge module, except CKSYN, supports clock gating by generating a busy signal whenever there are outstanding accesses being handled.

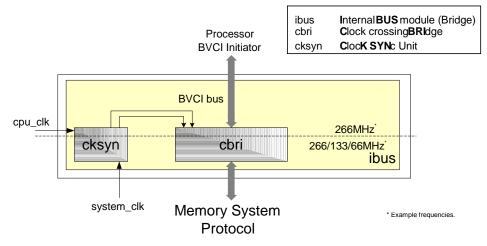

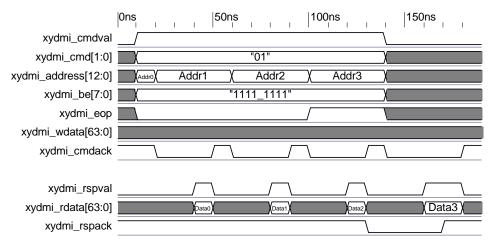

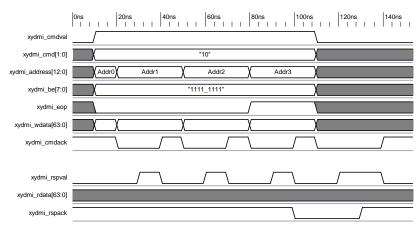

# **Clock Synchronization Unit**

The Clock Synchronization Unit, called CKSYN, is used to provide synchronization signals to the bridge so as to ensure that data on the BVCI bus can be transferred correctly across the clock domain. This module generates a synchronization signal to support processor clock to system clock frequency ratios of 1:1, 2:1, 3:1 and 4:1. Both clocks must be phased locked.

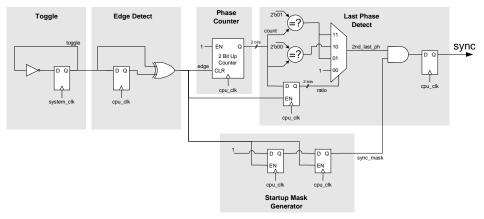

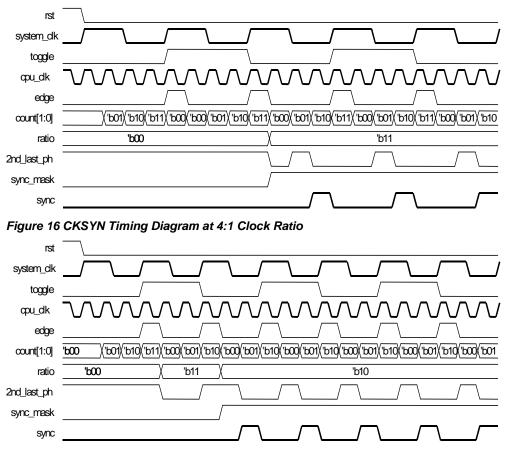

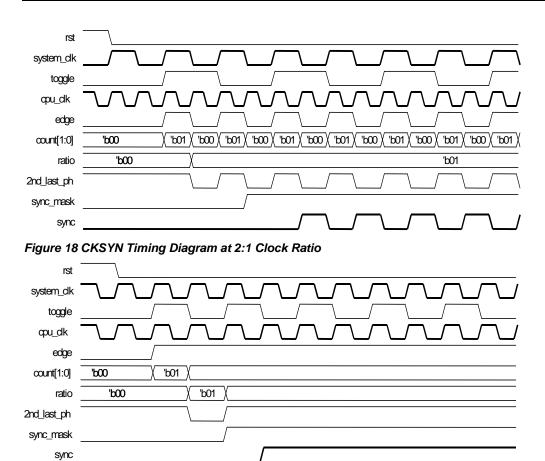

Figure 15 shows the design of the clock synchronization unit.

#### Figure 15 Design of the CKSYN

The CKSYN unit is used to generate a pulse on the synchronization signal (sync) that correspond to the last main clock period that resides in the system clock domain. It does this without having to resort to the use of the clock signals themselves as input signals, and without the need for the user to configure the hardware via software programmable registers or via configurations during RTL generation. This allows the module to be placed and routed without special consideration, allowing the user to avoid complicated issues often related to using clocks as signals, and easing the task of choosing or changing the system bus frequency throughout the SoC development cycle.

The CKSYN uses a number of logic units to generate the synchronization signal.

- <u>Toggle Unit</u>

- Edge Detection

- Phase Detection

- Mask Generator

- Last Phase Detect

### **Toggle Unit**

The Toggle Unit generates a toggle signal (toggle) that changes at every rising edge of the system clock (clk\_sys).

#### **Edge Detection**

The Edge Detect unit detects the rising edge of the toggle signal on the CPU clock domain. This edge signal (edge) will always go high at the first CPU clock (clk\_cpu) period within a system clock period (clk\_sys).

#### **Phase Detection**

The Phase Counter Unit counts up continuously and gets cleared whenever the edge signal is high. Hence the counter always counts up to one less than the number of CPU clock cycles that fit in the system clock cycle. Therefore, for example, for a CPU clock to system clock frequency ratio of 4:1, the counter counts continuously from 0 to 3. The range of clock ratios supported is dependent on the width of the counter, with the largest ratio supported at  $2^{N}$ :1 for a N bit counter. For the bridge to support up to 4:1, the counter only needs to be two bits wide.

#### Mask Generator

The Startup Mask Generator unit is basically a 2-bit shift register that turns the synchronization mask off  $(sync_mask = 1)$  after two detected edges of the toggle signal. This mask is used to block incorrect synchronization signal that can be generated during the start-up of this module after global reset.

### Last Phase Detect

The Last Phase Detect unit is used to generate a pulse at the last CPU clock cycle within the system clock cycle. Since it only needs to support up to 4:1 clock ratios, this module has been simplified. A 2-bit register is used to capture the count value at every toggle edge and it (ratio) represents the clock ratio of the two different clocks, with "00" representing 1:1, "01" representing 2:1, "10" representing 3:1 and "11" representing 4:1. This value is then used to select from four different pulses that are generated, (each pulse refers to a specific clock ratio). The first pulse type is for ratio 1:1 where the pulse is always on. The second pulse type is for ratio 2:1, where the signal is set to high every time the count value is at "01". The third pulse type is for ratio 3:1, where the signal is set to high when the count value is "00". Finally the fourth pulse type is for ratio 4:1, where the signal is set to high when the AND gate, and registered to become the synchronization (sync) output.

NOTE During global reset, all flops, registers and the counter are set to zero.

Figure 16, Figure 17, Figure 18 and Figure 19 show four example timing diagrams when dealing with 4:1, 3:1, 2:1 and 1:1 clock ratios respectively.

Figure 17 CKSYN Timing Diagram at 3:1 Clock Ratio

Figure 19 CKSYN Timing Diagram at 1:1 Clock Ratio

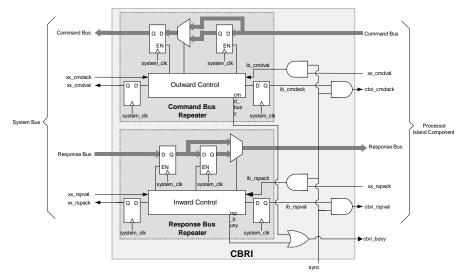

# **Clock Crossing BVCI Bridge**

The CBRI is used to convert accesses between the two clock domains ( $clk_cpu$  and  $clk_sys$ ). The supported frequency ratios of  $clk_cpu$  to  $clk_sys$  are 1:1, 2:1, 3:1 and 4:1, in the bridge module. However, this sub-module can support any ratios as long as the CPU clock is the same or higher frequency than system clock, and where it is higher, it is multiple times the frequency of the system clock. Both clocks have to be phased locked and clock tree balanced. This module is also responsible for isolating the timing of the internal bus and the BVCI System Bus from each other.

The CBRI cannot perform data packing and unpacking when converting access from one clock domain to another, and therefore, is essentially a bus repeater. It is capable of handling the crossing clock domain with the help of the CKSYN unit.

#### Figure 20 Design of the CBRI - Resets Not Shown

The CBRI is made up of a number of logic units:

- A command bus repeater module, used to deal with the command bus timing isolation.

- A response bus repeater module, used to deal with the response bus timing isolation

- Handshaking gating logic, used to ensure correct handshaking when crossing the clock domain

- An OR gate to combine the busy signals from the two repeaters.

# Chapter 4 — Bus Interfaces

This section summarizes the signal naming convention for the various processor island components that attach to the bus bridges, as well as the bus bridge interface to the external memory system for the following modules:

- Instruction Cache (MWIC) to Memory Bus System (via Bus Bridge)

- DMP to Memory Bus System (via Bus Bridge)

For additional information on alternative CPU Island interfaces see AHB Bus Bridge Reference, AXI Bus Bridge Reference, and ARC Legacy Bus Bridge Reference.

# Instruction Cache (MWIC) to Memory Bus System (via Bus Bridge)

The instruction cache (MWIC) does not connect directly to the memory bus systems. An intermediate bus bridge is used as shown in the following sections:

- <u>MWIC and Bus Bridge Block Diagram</u>

- MWIC to Bus Bridge Signal List

- <u>MWIC Bus Bridge to External Bus System Signal List</u>

- MWIC Unimplemented Signal List

- Big-Endian Configuration

- Interface Timing

## **MWIC and Bus Bridge Block Diagram**

Figure 21 Instruction Cache to IBUS

## **MWIC to Bus Bridge Signal List**

The following MWIC Bus Bridge interface signals are internal to the processor island and will *not* appear on the CPU Island:

| Name         | Direction | Width | Description                                                                                     |

|--------------|-----------|-------|-------------------------------------------------------------------------------------------------|

| mwic_rspack  | Input     | 1     | Acknowledgement from the MWIC to say that it has received a valid 64-bit data item. Active High |

| mwic_cmdval  | Input     | 1     | Validates the command cell. Active High                                                         |

| mwic_eop     | Input     | 1     | Signifies end of packet and only asserted on the fourth and final command cell. Active High     |

| mwic_address | Input     | 32    | Physical byte address of instruction word to be fetched                                         |

| mwic_cmdack  | Output    | 1     | This is the signal from the bus bridge that acknowledges the receipt of a valid command         |

| mwic_rdata   | Output    | 64    | This is the returning 64-bit instruction word returning from the bus bridge.                    |

| Name        | Direction | Width | Description                                                                                     |

|-------------|-----------|-------|-------------------------------------------------------------------------------------------------|

| mwic_rspval | Output    | 1     | Validates 'mwic_rdata'                                                                          |

| mwic_rerror | Output    | 1     | Response error. Bus errors are transferred directly to the ARC 700 core via the BVCI interface. |

### **MWIC Bus Bridge to External Bus System Signal List**

The following MWIC Bus Bridge interface signals may appear on the CPU Island:

| Name         | Direction | Width | Description                                                                                                 |

|--------------|-----------|-------|-------------------------------------------------------------------------------------------------------------|